# Fault Diagnosis of Analog Circuits with Tolerances Using Artificial Neural Networks

## Ying Deng<sup>1</sup>, Yigang He<sup>1</sup> and Yichuang Sun<sup>2</sup>

College of Electrical and Information Engineering, Hunan University,410082, Changsha, China

Department of Electronic, Communication and Electrical Engineering ,Faculty of Engineering and Information Science, University of Hertfordshire, Hatfield Herts AL10 9AB,United Kingdom

#### Abstract

This paper proposes a method for analog fault diagnosis using neural networks. The primary focus of the paper is to provide robust diagnosis using a mechanism to deal with the problem of component tolerances and reduce testing time. The proposed approach is based on the k-fault diagnosis method and artificial backward propagation neural network. Simulation results show that the method is robust and fast for fault diagnosis of analog circuits with tolerances.

#### I. Introduction

For several decades, fault diagnosis of analog circuits, the forefront of modern circuit research, has gained wide attention in the testing arena [1-6]. However, component tolerances, non-linearities and poor fault models make fault location very complicated. Generally, component tolerances make the parameters of circuit elements uncertain and the computational equations of traditional methods complex. The non-linear characteristic of the relation between the circuit and its constituent elements makes it even more difficult to diagnose faults on-line and may lead to false diagnosis. To overcome these problems, a robust and fast fault diagnosis method taking tolerances into account is thus needed.

Artificial neural networks (ANNs) have been applied in many areas such as pattern recognition, signal and image processing, etc [5,6]. ANNs have the advantages of large-scale parallel processing, parallel storing, robust adaptive learning, and on-line computation. They are ideal for fault diagnosis of analog circuits with tolerances [5].

This paper proposes an ANN based method for fault diagnosis of analog circuits with tolerances. Section II

describes ANNs (especially backward propagation neural networks). Section III discusses the theoretical basis and framework of analog fault diagnosis. The new method is described in Section IV and examples are presented in Section V. Finally, conclusions are given in Section VI.

#### **II.** Artificial Neural Networks

In recent years, ANNs have received great attention in many aspects of scientific research and have been applied successfully in various fields such as chemical processes, digital circuitry, control systems, etc, for ANNs provide a mechanism for adaptive pattern classification. Even in unfavorable environments, they can still have robust classification. It should be stressed that choosing a suitable ANN architecture is vital for the successful application of ANNs. To date the most popular ANN architecture is the backward propagation neural network (BPNN). One of the significant features of neural networks when applied in fault diagnosis and testing is that on-line diagnosis is fast once the network is trained. In addition, ANN classifiers require fewer fault features than traditional classifiers. Further, neural networks are capable of performing fault classification at hierarchical levels.

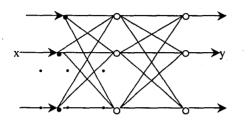

Based on learning strategies, ANNs fall into two categories: supervised and unsupervised. The BPNN is a supervised network. Typical BPNNs have two or three layers of interconnecting weights. Fig. 1 shows a standard two-layer network. Each input node is connected to a hidden layer node and each hidden node is connected to an output node in a similar way. This makes the BPNN a fully connected network topology. Learning takes place during the propagation of input patterns from the input nodes to the output nodes. The outputs are compared with the desired target values and an error is produced. Then the weights are adapted to minimize the error. Since the desired target values are known, this is a supervised learning process.

Fig.1 BPNN architecture

In Fig.1, input x=[x0, x1, ..., xm-1] and output y=[y0, y1, ..., yn-1]. The hidden layer and the output layer can be described as a general layer. The relation of output Oi<sup>(1)</sup> and input Oj<sup>(1-1)</sup> of layer j is defined as:

| Oi <sup>(1)</sup> =fs[Ii <sup>(1)</sup> ]   | (1) |

|---------------------------------------------|-----|

| $Ii^{(l)} = \Sigma W_{ij}^{(l)} Oj^{(l-1)}$ | (2) |

Equation (1) can be transformed into

$F_{s}(I)=1/(1+\exp(-I))$

The initial values of weights are assumed to be random numbers evenly distributed between -0.5 and 0.5; and the weight between the j<sup>th</sup> neuron of the (k-1)<sup>th</sup> layer and the i<sup>th</sup> neuron of the k<sup>th</sup> layer is defined as  $W_{i,j,k}$ . The weight adaptation equation is given by

(3)

$W_{i,j,k}(t_n) = W_{i,j,k}(t_{n-1}) - \alpha E(t_n) / W_{i,j,k}(t_{n-1}) + \eta \cdot \Delta W_{i,j,k}(t_{n-1}) \quad (4)$ where  $0 < \alpha < 1$ ,  $0 < \eta < 1$  and  $E = 1/2\Sigma(y_i - b_i)^2 \quad i = 1 \dots n$

It can be seen that BP neural networks have the following ideal advantages for fault diagnosis with tolerance:

- 1) Even in noisy environments, recognition of classes can be still achieved by the BP classifier.

- 2) BPNNs have the function of recalling and the capability to gain the complete fault features from the fragmentary features.

## III Fault Diagnosis Of Analog Circuits With Tolerances

The methods for analog fault diagnosis fall into two categories: simulation before test (SBT) and simulation after test (SAT). The k-fault diagnosis method [1-4] belongs to the SAT category. This method assumes that there are k faults in the circuit and requires that the number of accessible nodes, m is larger than k. The method can effectively locate faults in circuits without tolerances. But to the circuits with tolerances, the testing process is slow and ambiguous. In order to improve the on-line characteristic and achieve robustness of diagnosis, we present a new method which combines the k-fault diagnosis method with the highly parallel processing BPNN in the next section.

## **IV. Application Of BPNN To Fault Diagnosis**

Using BPNNs to diagnose faults in analog circuits with tolerances involves choosing the neural network structure, generating fault features and forming training groups.

Let us consider a circuit that has d elements. The nominal value of component i is denoted as  $y_{io}$  and the actual value  $y_i$ . The deviation caused by tolerance and fault is  $\Delta y_i = y_i \cdot y_{io}$ . Using the k-fault method, we select m=k+1 testing nodes according to the topology of the circuit. With the excitation current, we can calculate the nominal values of the testing node voltages as  $[V_o] = [V_{1o}, V_{2o}, ..., V_{mo}]^T$ . We can also measure the actual voltages of the testing nodes as  $[V_m] = [V_1, V_2, ..., V_m]^T$ . The incremental voltages due to tolerance and fault can then be calculated as

$[\Delta V_m] = [V_m] - [V_0] = [\Delta V_1, \Delta V_2, ..., \Delta V_m]^T$ where  $\Delta V_1 = V_i - V_{i_0}$ .

### A. Structure and algorithm of BPNN

The single hidden layer, m input and d output neural network is adopted. As far as the hidden neurons are concerned, the number of hidden neurons is determined by the complexity of the circuit and the difficulty in classifying the faults. Generally speaking, the more elements in the circuit, the more hidden nodes needed. When training the BP neural network, we first select

293

several hidden nodes, and if the required precision can not be reached, then more hidden nodes are added. The activation function of the neurons is defined as:  $y=1/(1+e^x)$

The initial values of the interconnecting weights are random numbers that fall within [-0.5, 0.5].

The algorithm of BP neural networks is modified to decrease the time spent on training the network, described by  $W_{i,j,k}(n+1)=W_{i,j,k}(n)-\gamma E(n+1)/W_{i,j,k}(n)+\beta \Delta W_{i,j,k}(n)$  where  $\beta$  is the inertial factor and its value is 0.9;  $W_{i,j,k}$  represents the interconnecting weight between the j<sup>th</sup> neuron of  $(k-1)^{th}$  layer and the i<sup>th</sup> neuron of the k<sup>th</sup> layer; E(n) means n times of the accumulative error function;  $\gamma>0$  and is slightly bigger than 1.

#### **B.** Fault Feature Generation

The k-fault method mainly exploits the spatial characteristic of measured voltage increments  $[\Delta V_m]$  to locate faults among all circuit elements. Therefore,  $[\Delta V_m]$  are selected to be the inputs with a dimension of m, of the established BPNN and the outputs of the BPNN correspond to the circuit elements, having a dimension of d. If the voltage value of the output node is tested as 1v, we deem that the corresponding element is faulty, otherwise, if 0v, we consider the element to be non-faulty.

## C. Constitution Of The Training Groups

In k-fault diagnosis, the tolerance influences the space characteristic of  $[\Delta V_m]$ , that is, the inputs of the BPNN. In the BPNN used, our specimen for training have been chosen to have a small ratio of fault to tolerance and are therefore representative for tolerance effects. This is the case that faults are comparatively difficult to detect. For hard faults, each component can be either open-circuited or short-circuited, the minimum simulation groups with 2d single faults are formed. First, several groups are tested, then the ones which can not be correctly located are added to the training specimen groups to be trained again, until satisfactory diagnosis results are obtained.

### **v.** Examples

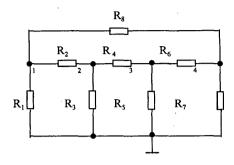

Simulation of the proposed method has been carried out for the circuit in Fig.2 using Pspice.

Fig.2 A resistive circuit

In Fig.2, there are 8 resistors. The nominal value of each resistor is 1  $\Omega$ , and each element has a tolerance of  $\pm 5\%$ . Suppose that a single soft fault has occurred in it. According to the topology of the circuit, three testing nodes are selected, which are numbered nodes 1, 3 and 4. Thus, the BPNN should have 3 input nodes in the input layer and 8 output nodes in the output layer. In addition, 2 hidden layers with 8 hidden nodes each are designed. Programmed in C language, the BPNN algorithm has been simulated by computer. Also, Pspice is used to simulate the circuit and obtain  $\Delta U_m$ . Because the diagnosis principle is the same for every resistor in the circuit, we arbitrarily select R<sub>3</sub> as an example to demonstrate this new method.

The sample feature values of  $R_3(X_0, X_1, X_2)$  have been calculated and shown in Table 1. These sample feature

Table 1 Sample feature values of R<sub>3</sub>

|                | Xo      | X <sub>1</sub> | X <sub>2</sub> |

|----------------|---------|----------------|----------------|

| R <sub>3</sub> | 0.6396  | 0.6396         | 0.4264         |

|                | -0.6396 | -0.6396        | -0.4264        |

values of  $R_3$  are input to the BPNN in order that the BPNN is trained and can memorize the information learned before. After over 5,000 times of training and when the overall error is less than 0.03, the training of the BPNN is completed and the knowledge of the sample features are stored in it.

Now suppose  $R_3$  is faulty and when it is  $0.2 \Omega$ ,  $0.9 \Omega$ ,  $1.2 \Omega$ , and  $2.5 \Omega$  respectively, the values of the other resistors are within the tolerances range of  $\pm 5\%$  (Here the values of the 7 resistors are selected arbitrarily as

$R_1=1.04 \Omega$ ,  $R_2=0.99 \Omega$ ,  $R_4=1.02 \Omega$ ,  $R_5=0.98 \Omega$ ,  $R_6=1.01 \Omega$ ,  $R_7=0.987 \Omega$ ,  $R_8=0.964 \Omega$ ). With the excitation of 1A current to testing node 1, the actual feature values of the three testing nodes are obtained by getting  $\Delta U_m$  and calculating the left part of equation (8). Then the actual feature values ( $X_0$ ,  $X_1$ ,  $X_2$ ) of the four situations are input to the input nodes of the BPNN respectively to classify and locate the corresponding faulty element. Table 2 has shown the results.

| R <sub>3</sub><br>value | Xo          | X           | X <sub>2</sub> | Output<br>node<br>No.3<br>(R <sub>3</sub> )<br>value | Max<br>value in<br>the<br>other<br>output<br>nodes |

|-------------------------|-------------|-------------|----------------|------------------------------------------------------|----------------------------------------------------|

| 0.2 Ω                   | -<br>0.6486 | -<br>0.6305 | -<br>0.4264    | 0.8495                                               | 0.1195                                             |

| 0.9Ω                    | -<br>0.6529 | -<br>0.6233 | -<br>0.4304    | 0.8491                                               | 0.1194                                             |

| 1.2 Ω                   | 0.6439      | 0.6352      | 0.4260         | 0.9480                                               | 0.0569                                             |

| 2.5 Ω                   | 0.6482      | 0.6412      | 0.4259         | 0.9510                                               | 0.0546                                             |

| Table 2 Results of BPNN in diagnosi | is |  |

|-------------------------------------|----|--|

|-------------------------------------|----|--|

From Table 2, it can be found that the diagnosis result is correct. For output node 3 the value of the output layer is more than 0.5, and that of the other output nodes are less than 0.5, which shows that  $R_3$  is the faulty element. Also, when  $R_3$  is 0.9  $\Omega$ , which is the case that the fault is very small and comparatively difficult to detect, the BPNN based k-fault diagnosis method can still successfully locate it. Further, for the other 7 resistors, the new method has also been proven to be effective by our simulation. In addition, it can be found that once the BPNN is trained, the diagnosis process becomes very simple and fast.

Compared with the traditional k-fault diagnosis method, the proposed BPNN-based method has clear advantages. The BPNN-based k-fault method requires less computation and very fast. Computation is needed only once to obtain sufficient sample and actual feature values of testing nodes for a particular circuit. Also, the problem of component tolerance can be successfully handled by the robustness of BPNN. Hence the new diagnosis method is more robust and faster and can be used in real-time testing.

#### VI. Conclusions

A method for fault diagnosis of analog circuits with tolerances using ANNs has been proposed. This method is

robust to component tolerances and requires small after-test computation time. The diagnosis of hard faults in linear circuits with tolerances has been shown, although the method is also suitable for soft faults and nonlinear circuits. Significant diagnosis precision has been be reached by training a large number of specimen in the BPNN. While the faulty specimen trained can be easily identified, the BPNN can also detect untrained faulty specimen. Therefore the fault diagnosis method presented in this paper can not only quickly detect the faults in the traditional dictionary but also the faults not in the dictionary.

#### Acknoledgements

This work is supported by the Natural Science Youth Funding Council of China under Grant No.59707002, Hunan Natural Science Funding Council, and Science and Technology Key Research Projects of Education Committee of China.

#### Refrences

J. W. Bandler, "Fault diagnosis of analog circuits," Proceedings of IEEE, Vol.73, No.8, pp.1279-1325., 1985,

R. W. Liu, ed., Testing and Diagnosis of Analog

Circuits and Systems, Van Nostrand Reinhold, 1991.

[3] Y. Sun and J. K. Fidler, "A topological method of class-fault diagnosis," Proc. IEEE Midwest Symp. on Circuits and Systems, Washington D C, USA, 1992.

[4] Y. Sun, "Cut-fault diagnosis of nonlinear circuits," Proc. China Int. Conf. on Circuits and Systems, Nanjing, China, 1989.

[5] R. Spina and S. Upadhyaya, "Fault diagnosis of analog circuits using artificial neural networks as signature analyzers," in Proc. Rochester Int. ASIC Conf., Sept, 1992, pp. 357-362

[6] Y.G. He, X.J. Luo, G.Y. Qiu, A neural-based nonlinear L1-norm optimization algorithm for diagnosis of networks, J. of Electronics, Vol.15,No.4, ,pp365-371,1998