### Automatic Code-Generation Techniques for Micro-Threaded RISC Architectures

Jason M<sup>c</sup>Guiness

Submitted to the University of Hertfordshire in partial fulfillment of the requirements of the degree of Master of Science by Research.

Compiler Technology and Computer Architecture Group, Department of Computer Science Sciences, University of Hertfordshire, England. July 2006

### Dedicated to

the many enlight ening discussions I had with Dr. Richard Harris and Dr. And res Márquez.

### Automatic Code-Generation Techniques for Micro-Threaded RISC Architectures

Jason M<sup>c</sup>Guiness

Submitted to the University of Hertfordshire in partial fulfillment of the requirements of the degree of Master of Science by Research. July 2006

#### Abstract

There has been an ever-widening gap between processor and memory speeds, resulting in a 'memory wall' where the time for memory accesses dominates performance. To counter this, architectures that use many very small threads that allow multiple memory accesses to occur in parallel have been under investigation. Examples of these architectures are the CARE (Compiler Aided Reorder Engine) architecture, micro-threading architectures and cellular architectures, such as the IBM Cyclops family, implementing using processors-in-memory (PIM), which is the main architecture discussed in this thesis. PIM architectures achieve high performance by increasing the bandwidth of the processor to memory communication and reducing that latency, via the use of many processors physically close to the main memory. These massively parallel architectures may have sophisticated memory models, and I contend that there is an open question regarding what may be the ideal approach to implementing parallelism, via using many threads, from the programmer's perspective. Should the implementation be at language-level such as UPC, HPF or other language extensions, alternatively within the compiler using trace-scheduling? Or should it be at a library-level, for example OpenMP or POSIX-threads? Or perhaps within the architecture, such as designs derived from data-flow architectures? In this thesis, DIMES (the Delaware Iterative Multiprocessor Emulation System), which is being developed by CAPSL at the University of Delaware, was used as a hardware evaluation tool for such cellular architectures. As the programing example, the author chose to use a threaded Mandelbrot-set generator with a work-stealing algorithm to evaluate the DIMES *cthread* programming model. This implementation was used to identify potential problems and issues that may occur when attempting to implement massive number of very short-lived threads.

## Declaration

The work in this thesis is based on research carried out at the Compiler Technology and Computer Architecture Group, University of Hertfordshire, England. No part of this thesis has been submitted elsewhere for any other degree or qualification and it is all my own work unless referenced to the contrary in the text.

### Acknowledgments

My sincere thanks to Dr. Colin Egan my final supervisor, of the University of Hertfordshire, for taking on an unusual student! But also my thanks to Professor Alex Shafarenko, of the same University for his inspirational conversations, and being instrumental in my collaboration with CAPSL and the University of Delaware. Finally, my thanks to Dr. Slava Muchnick, who initiated this program of research. The following doctors also deserve honorable mention: Dr. Andres Márquez and Dr. Georg Munz. Both were inspirational conversationalists, each in their own ways...

The research presented in this thesis was, in part, supported by the Engineering and Physical Research Council (EPSRC) grant number: GR/S58492/01.

## Contents

|          | Abstract                                                             |                                                              |    |  |  |  |  |  |

|----------|----------------------------------------------------------------------|--------------------------------------------------------------|----|--|--|--|--|--|

|          | Declaration                                                          |                                                              |    |  |  |  |  |  |

|          | Acknowledgments                                                      |                                                              |    |  |  |  |  |  |

| 1        | Introduction                                                         |                                                              |    |  |  |  |  |  |

| <b>2</b> | $\mathbf{Rel}$                                                       | ated Work 6                                                  |    |  |  |  |  |  |

|          | 2.1                                                                  | The VLIW Origins                                             | 6  |  |  |  |  |  |

|          | 2.2 Beyond VLIW: Super-scalar: the combination of branch predictors, |                                                              |    |  |  |  |  |  |

|          |                                                                      | speculation and memory hierarchies                           |    |  |  |  |  |  |

|          | 2.3                                                                  | Parallel Architectures                                       | 9  |  |  |  |  |  |

|          |                                                                      | 2.3.1 EARTH, the EARTH compiler and CARE                     | 10 |  |  |  |  |  |

|          |                                                                      | 2.3.1.1 The EARTH architecture                               | 10 |  |  |  |  |  |

|          |                                                                      | 2.3.1.2 The EARTH Compiler                                   | 10 |  |  |  |  |  |

|          |                                                                      | 2.3.1.3 The CARE Architecture                                | 12 |  |  |  |  |  |

|          |                                                                      | 2.3.2 The Micro-Threaded Architecture                        | 12 |  |  |  |  |  |

|          |                                                                      | 2.3.3 IBM BlueGene/C and Cyclops                             | 14 |  |  |  |  |  |

| 3        | The                                                                  | e limitations of super-scalar architectures: the memory wall | 16 |  |  |  |  |  |

|          | 3.1                                                                  | Multiple cores and massively parallel architectures          | 17 |  |  |  |  |  |

|          | 3.2 The programming models: from compilers to libraries              |                                                              |    |  |  |  |  |  |

|          | 3.3                                                                  | IBM BlueGene/C, Cyclops and DIMES/P: the implementation of a |    |  |  |  |  |  |

|          | cellular architecture                                                | 20                                                           |    |  |  |  |  |  |

|          | 3.4                                                                  | Programming Models on Cellular Architectures                 | 21 |  |  |  |  |  |

|              | 3.5                                                            | Programming for Cyclops                                         | 22    |  |  |

|--------------|----------------------------------------------------------------|-----------------------------------------------------------------|-------|--|--|

| 4            | 4 Programming the Mandelbrot Set Algorithm for Cyclops         |                                                                 |       |  |  |

|              | 4.1 An Introduction to the Mandelbrot Set                      |                                                                 |       |  |  |

|              | 4.2                                                            | Threading and the Mandelbrot Set                                | 27    |  |  |

|              | 4.3 A Discussion of the Work-Stealing Algorithm 5              |                                                                 | 30    |  |  |

|              | 4.4 DIMES/P Implementation of the Mandelbrot-set application . |                                                                 | 31    |  |  |

|              |                                                                | 4.4.1 The Memory Layout                                         | 33    |  |  |

|              |                                                                | 4.4.2 The Host Interface                                        | 33    |  |  |

|              |                                                                | 4.4.3 Execution details of the Mandelbrot-set application       | 34    |  |  |

| <b>5</b>     | List of Achievements 3                                         |                                                                 |       |  |  |

| 6            | 5 Summary<br>Bibliography<br>Appendix                          |                                                                 |       |  |  |

|              |                                                                |                                                                 |       |  |  |

|              |                                                                |                                                                 |       |  |  |

| $\mathbf{A}$ | Imp                                                            | lementing Applications on a Cellular Architecture - the Mandell | orot- |  |  |

|              | set.                                                           |                                                                 | 57    |  |  |

|              | A.1                                                            | Abstract.                                                       | 57    |  |  |

|              | A.2                                                            | Introduction.                                                   | 58    |  |  |

|              | A.3                                                            | Programming Models on Cellular Architectures                    | 60    |  |  |

|              | A.4                                                            | $Conclusion/Discussion. \ . \ . \ . \ . \ . \ . \ . \ . \ . \$  | 60    |  |  |

| в            | Imp                                                            | lementing Applications on a Cellular Architecture - the Mandell | orot- |  |  |

|              | set.                                                           |                                                                 | 61    |  |  |

|              | B.1                                                            | Overview:                                                       | 61    |  |  |

|              | B.2                                                            | A recap on the memory wall. Part I:                             |       |  |  |

|              |                                                                | The processor viewpoint                                         | 62    |  |  |

|              | B.3                                                            | A recap on the memory wall. Part II:                            |       |  |  |

|              |                                                                | The memory viewpoint.                                           | 63    |  |  |

|              | B.4                                                            | The memory wall and cellular architectures: a solution?         | 63    |  |  |

|                                                                     | B.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Progra                                   | amming models on Cellular Architectures                                                    | 64 |  |  |  |

|---------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|--------------------------------------------------------------------------------------------|----|--|--|--|

|                                                                     | B.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | A brie                                   | f overview of Cyclops and DIMES/P-2                                                        | 65 |  |  |  |

|                                                                     | B.7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | An int                                   | roduction to the Mandelbrot set                                                            | 65 |  |  |  |

|                                                                     | B.8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | The cl                                   | assic algorithm used to generate the Mandelbrot set:                                       | 66 |  |  |  |

|                                                                     | B.9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Thread                                   | ding applied to the Mandelbrot set                                                         | 67 |  |  |  |

| B.10 The Render-Thread Algorithm                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                          | ender-Thread Algorithm                                                                     | 67 |  |  |  |

|                                                                     | B.11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | The W                                    | Vork-Stealing Algorithm                                                                    | 68 |  |  |  |

| B.12 A Discussion of the Work-Stealing Algorithm.                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                          |                                                                                            | 69 |  |  |  |

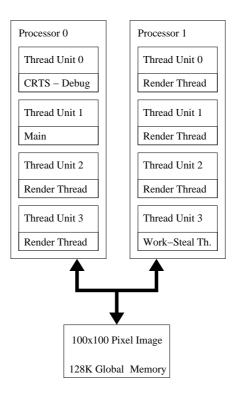

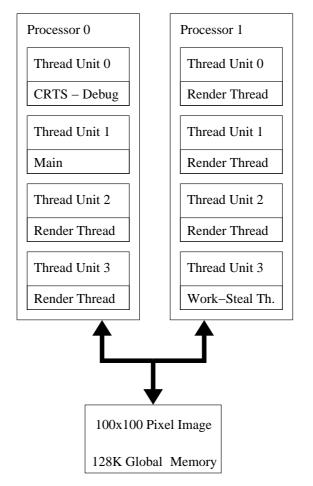

| B.13 The static layout of the render and work-stealing threads with |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                          |                                                                                            |    |  |  |  |

|                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | DIME                                     | S/P-2 system is shown below:                                                               | 70 |  |  |  |

|                                                                     | B.14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Execu                                    | tion Details of the Mandelbrot-set application.                                            | 70 |  |  |  |

|                                                                     | B.15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Supero                                   | computing Benchmarks: Global Updates Per Second (GUPS).                                    | 70 |  |  |  |

|                                                                     | B.16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | GUPS                                     | and DIMES                                                                                  | 71 |  |  |  |

|                                                                     | B.17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3.17 Limitations of current GUPS & DIMES |                                                                                            |    |  |  |  |

|                                                                     | B.18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Conclu                                   | usion & Future Work                                                                        | 72 |  |  |  |

| C The Challenges of Efficient Code-Generation for Massively Par     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                          |                                                                                            |    |  |  |  |

|                                                                     | Arc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | hitectı                                  | ires.                                                                                      | 74 |  |  |  |

| C.1 Abstract                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                          |                                                                                            | 74 |  |  |  |

|                                                                     | C.2       Introduction       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       . |                                          |                                                                                            |    |  |  |  |

|                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                          |                                                                                            |    |  |  |  |

|                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | C.3.1                                    | The Programming Models: from Compiler to Libraries                                         | 76 |  |  |  |

|                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | C.3.2                                    | Programming Models on Cellular Architectures                                               | 77 |  |  |  |

|                                                                     | C.4 Programming for Cyclops - <i>cthreads</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                          | amming for Cyclops - <i>cthreads</i>                                                       | 78 |  |  |  |

|                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | C.4.1                                    | Threading and the Mandelbrot Set                                                           | 79 |  |  |  |

|                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | C.4.2                                    | $\operatorname{DIMES}/\operatorname{P}$ Implementation of the Mandelbrot-set application . | 80 |  |  |  |

|                                                                     | C.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Discus                                   | sion                                                                                       | 80 |  |  |  |

# List of Figures

| $P(n)$ for conventional memory with $L_0 = 1/T_0$ , taken from [13]          | 13                                                                                                  |

|------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|

| Schematic of a micro-threaded, RISC architecture                             | 14                                                                                                  |

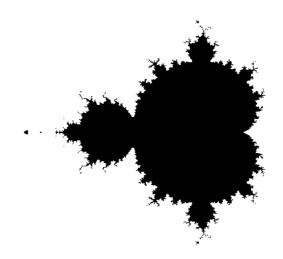

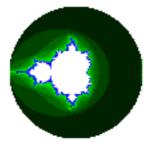

| The classic Mandelbrot set image generated by "Fractint" [119]. Points       |                                                                                                     |

| coloured black are in $M$                                                    | 26                                                                                                  |

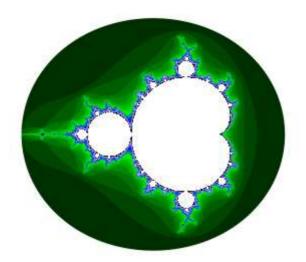

| A false-colour image of the Mandelbrot set generated by "Aleph One"          |                                                                                                     |

| [71]                                                                         | 27                                                                                                  |

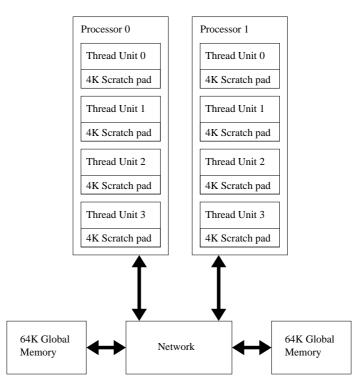

| Simplified schematic overview of the DIMES/P implementation of               |                                                                                                     |

| CyclopsE                                                                     | 31                                                                                                  |

| Layout of the render and work-stealing threads within the $\mathrm{DIMES/P}$ |                                                                                                     |

| system                                                                       | 32                                                                                                  |

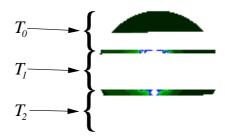

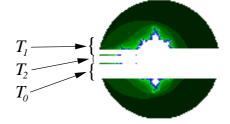

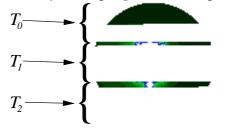

| The image generated shortly after program start-up.                          | 34                                                                                                  |

| Image generation has progressed, shortly before a work-stealing event.       | 34                                                                                                  |

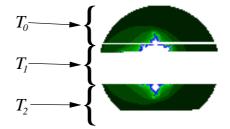

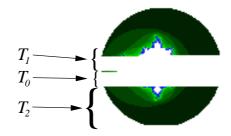

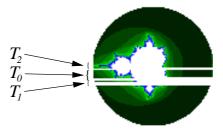

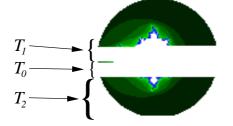

| Just after the first work-stealing operation                                 | 35                                                                                                  |

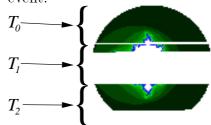

| The second work-stealing operation                                           | 35                                                                                                  |

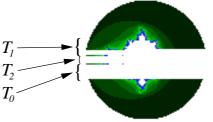

| The third work-stealing operation                                            | 35                                                                                                  |

| The completed Mandelbrot set                                                 | 36                                                                                                  |

| The image generated shortly after program start-up.                          | 71                                                                                                  |

| Image generation has progressed, shortly before a work-stealing event.       | 71                                                                                                  |

| Just after the first work-stealing operation                                 | 71                                                                                                  |

| The second work-stealing operation                                           | 71                                                                                                  |

|                                                                              | The classic Mandelbrot set image generated by "Fractint" [119]. Points<br>coloured black are in $M$ |

### Chapter 1

### Introduction

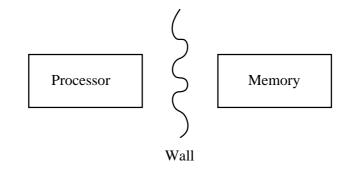

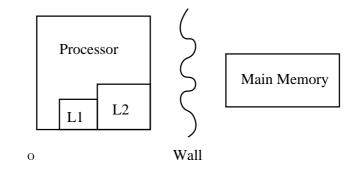

The memory-wall [121] is a limiting factor in CPU performance, which may be countered by introducing extra levels in the memory hierarchy [15, 121]. However, these extra levels increase the penalty associated with a miss in the memory-subsystem, due to memory-access times, limiting the ILP. Also, there may be an increase in design complexity and power consumption of the overall system. An approach to avoid this problem may be to fetch sets of instructions from different memory banks, i.e. introduce threads, which would allow an increase in ILP, in proportion to the number of executing threads. There are issues with introducing multiple threads of execution, such as they should not have data or control flow that is inter-dependent between any of the currently executing threads. Another issue is that the cost for creating, synchronising and destroying threads should be very cheap, which constrains the architectural design. The reason for this latter constraint is that the latencies to be mitigated against would be pipeline stalls, usually very short periods of time, potentially between a few to tens of clock cycles. Such short threads, that are designed to mitigate against pipeline stalls, this thesis shall term as *micro*threads. This definition is in slight contrast to the definitions used within [13, 68], where the motivation for the definition came from the differing size of the thread, i.e. that they lacked a stack and context. Given that the threads to which this thesis refers, and the threads of [13,68] are all used to maintain pipeline throughput, then this modified definition has some justification. Note that these micro-threads are not operating-system level threads, which have large context, are potentially preemptible and used for process-level parallelism. Micro-threads would be designed to have very little context, making creation and destruction cheaper.

Various architectures have been proposed that could support micro-threads:

- The architecture of [13,68], which is designed to support the smallest variant of micro-threads.

- The CARE (Compiler Aided Reorder Engine) architecture described in [75], that supports *strands*, a variant of micro-threads, that fulfil the same goal, thus come under the definition of micro-threads used in this thesis.

- The integration of processing logic and memory [21, 41, 105, 106] within the same chip, termed PIM. Such integration may also improve both data-processing and data-access time.

In this thesis the application of micro-threading to the final PIM architecture is what will be examined in most detail, with occasional references to the other architectures.

A problem with integrating processors and memory in the same space is that the processor speed and the amount of memory are reduced [21]. This may be overcome by connecting multiple, independent PIM cells, where the resultant architecture is described as cellular. In this multi-threaded organisation, every thread unit serves as an independent single-issue, in-order processor, thus able to potentially access memory independently, depending upon the exact details of the architectural design.

This gives rise to a number of code-generation problems, some of which are discussed in appendix C, centred around the fact that to provide computational power, these systems are massively parallel. It is common folklore in the programming community that writing correct and efficient multi-threaded programs is hard. This problem could be compounded for such cellular architectures. Thus, considerable research effort has been targeted at code generation, including thread generation, to support such hardware. There is likely to be much research to do: to develop compilers to generate multi-threaded code, create lower-level libraries that ease the burden of creating such code, and write debuggers that allow the programmer to effectively debug such programs. Thread-generating compilers exist; for example, HPF and UPC [45]. The Fortranbased HPF is very useful for mathematical problems, but less so for other problem domains. Both compilers specialise on parallelising loop-constructs. Other C and C++ parallelising compilers exist, but are largely based upon the OpenMP library, for example IBM XL Fortran and Visual Age C/C++, which also tend to focus upon loops and a source of parallelism. Alternatively, higher-level approaches, such as a compiler that may automatically create threads using the *split-phase constraint* exist for such architectures as EARTH [109]. The *split-phase constraint* may be loosely defined as when the compiler may generate a synchronization variable, and a destination thread for a potentially, long-latency load from remote memory. This EARTH compiler attempts to fulfil the promise of thread-generation for the programmer: it is automated, general-purpose - not limited to loops - and the schedules it creates are provably fast and correct.

Moreover, the different memory hierarchies within cellular architectures add to the multi-threaded code-generation problem. Research is in progress to address this problem: for example by placing hardware memory-banks that have different access and consistency models at different address ranges in the memory-map of the virtual machine, known as *location consistency* [40] is one approach. The EARTH compiler and UPC both provide language, hence compiler support, for such features using the split-phase constraint, or the use of the *strict* and *relaxed* keywords, respectively.

The library-based approach to threading has often been made less effective by a lack of language support, that would aid the expressiveness and use of thread-related constructs (for example threads themselves and synchronization mechanisms). For example, the use of pragmas in the various implementations of OpenMP, and the fact that general-purpose languages have been very slow to adopt a sufficiently so-phisticated abstraction of the features of any machine model. C/C++ has had the *volatile* keyword for over a decade, but has made very limited use of it in supporting shared data, that may be accessible by more than one thread, an obvious use of the keyword. (Indeed this use is to be introduced into the next C++ standard, to be finalised not before 2009.) This limitation has been noted (at the Association of C and C++ Users Conference, 2005, by B. Stroustrup, in one of his keynote presentations,

and by others) and has apparently hampered development of multi-threaded programs and the development of compilers that might automatically generate threads. The author contends that library-based solutions to threading are too dependant upon the programmer to use correctly. For example, the explicit use of locks in programs is prone to error, with deadlocks and race-conditions that are hard to track down are easily introduced.

The development of suitable tools to debug multi-threaded applications has been slow. Some tools are available (*strace, truss, pstack* and various debugger) but are very limited in functionality, with regards to threading. More useful debuggers are in development, for example for Cyclops [29]. But these are few, with currently limited functionality. Further development in this area would be vital to allow the programmer to debug their code on such systems. A more important aspect of these tools would be to aid the programmer with regards to reasoning about the function of their multi-threaded code, and thus avoid such bugs.

In the author's opinion, the leaders in this field are aiming at a language, not library, based solution, which would be the appropriate level of abstraction for the expression of parallelism within a program. The compiler support would allow the development of more powerful multi-threading abstractions, such as various algorithms, that would help to divorce the programmer from the complex details of the underlying architectural support. But there are limitations in the direction of such current compiler developments, for example, UPC apparently exposes only loop-based parallelism and HPF requires explicit statements within the code to make the compiler generate multi-threaded code which also directed towards parallelising loops. The author contends that this would be far too limited for application to general-purpose programs.

As identifying parallelism both correctly and efficiently has been very hard for the programmer to do, the author contends that they should not do it. When such massively-parallel architectures are developed, this process should include time to develop libraries that plug into the target compilers to allow them to generate efficient code for that architecture. Thus the programmer would identify variables and functions that they believe they may be able to parallelise, to guide the compiler. The compiler, equipped via these libraries with a detailed machine-model would be able to refine and hone these gross indications in the program to generate efficient code. The author experienced only limited effort investigating the software aspect of the code generation problem for massively parallel architectures. Unfortunately, if this case should continue, this shortcoming could adversely affect the popularity of such systems and maintain the perception that massively parallel architectures are too specialized and thus too expensive to be of more general use. Given the popularity of multi-core processors, this position is set to become even more untenable.

### Chapter 2

### **Related Work**

### 2.1 The VLIW Origins

The research that has been done in the field of multi-threaded architectures, may be considered to have been heavily influenced by the work on VLIW architectures: one can consider them to have a limited number of "live" threads at any one instant, limited not only by the number of slots in the instruction word, but also by the ability of the compiler to identify such instruction-level parallelism. Some research work [83,117] demonstrated that, in the SPEC95 benchmark suite, there has been potential for a large number of independent threads, up to the order of thousands.

Unfortunately this motivating result was for VLIW machine-models with certain, ideal parameters; a common limit has been the number of available registers, or bypass buses, or an oracle branch predictor within the compiler. This gave impetus to the architecture field to research these rich topics, and has provided very effective *dynamic*, rather than compile-time branch predictors. But the VLIW compilers, the trace compilers of the time, required a compile-time branch predictor to produce code that did not need expensive recovery mechanisms, and enable the compiler to perform the whole-program, code-motion optimizations it needed to do to extract the ILP from the programs. Results for the register problem have been similarly mixed: due to the multi-ported nature of the register banks, there is a physical and technological limit: having more registers scales the area of the chip linearly, but more register ports (for bypass buses) scales the area geometrically. Technological limitations in chip fabrication limit the yield of the chips: the larger the area, the lower the yield in direct proportion. Thus adding a sufficient number of register ports will always reach a limit in the current technological ability to produce economic quantities of such chips.

The instruction density in VLIW code decreased for various reasons:

- a lack of an effective compile-time branch predictor,

- combined with limited register resources,

- true data-dependencies,

- and structural hazards

all of which meant is was necessary to inject no-ops into the instruction stream. These no-ops have been of vital significance: they were a direct indication of the inefficiency of the compiler and tool-chain, hence architecture, to extract ILP from the instruction stream, and indicate an inefficiency of both the software and the compiler. Consequently the effectiveness of the VLIW architecture as a technique to increase performance, via extracting ILP, by re-compiling the source code had been constrained.

# 2.2 Beyond VLIW: Super-scalar: the combination of branch predictors, speculation and memory hierarchies

But the research yielded very useful results: the development of dynamic, as opposed to the compile-time branch predictors. These meant that speculative execution of code was much less likely to be wasted work. Thus the advent of super-scalar processors, but these had their problems: performance was hindered by slow memory speeds. So small caches were implemented, based upon the assumption of data and control locality. The size of a hardware cache has been chosen to be roughly 10% of the average size of the executing program the related data. These caches have

# 2.2. Beyond VLIW: Super-scalar: the combination of branch predictors, speculation and memory hierarchies 8

been composed of very high speed memory, which has been costly to implement. They were also placed directly in line with the IF stage of the pipeline, allowing very high-speed instruction-fetch from the cache, if there was a cache hit [80]. Also, regarding instruction fetch: the accuracy of the branch predictor and placing it very early in the pipeline has been vital. This is to allow the branch target addresses to be obtained (potentially via the BTC, or via a default prediction, or a dynamic predictor may be used) before the instructions that would generate the result of that branch condition. This allowed the instruction cache to pre-fetch cache-line sized amounts of instructions from slower hierarchies, using the pre-computed, predicted, branch-target address, and deliver them with minimal pipeline stalls to the IF stage. The data cache has been more complex, but the concept of implementing a small, write-back, high-speed amount of memory so that register writes would be directed to this memory has been relatively simple: it would act as a buffer to the lowerlevel, slower memories, and allow memory reads to be potentially serviced directly by the data cache instead of from the lower-level memory hierarchies. Another major factor has been out-of-order instruction execution: if there were sufficient processor resources, instructions could be executed in parallel, although they would be fetched in-order and potentially retired out-of-order. Moreover instructions that completed faster need not be held up by slower instructions that were ahead of them in the instruction stream. The use of a scoreboard or register file [59, 80] allowed the data-dependencies between registers to be dynamically computed whilst the instructions were in flight in the pipeline. When these caches were combined with branch prediction and speculation even more ILP, and performance, could be extracted from the input instruction stream. In these architectures, the retirement of instructions was linked to an architectural state (potentially implemented via a reorder buffer) that, if a mis-prediction occurred, would have to be rolled back, and the instruction fetch re-started from the alternative branch. Also, if a processor were to implement precise interrupts, for example to implement processor exceptions, then a similar roll-back, or completion, of in-flight instructions would need to occur to ensure that the processor would be in an architectural state that would be consistent with the sequential program state.

### 2.3 Parallel Architectures

The roll-back implicitly implemented within super-scalar architectures has been viewed as a problem: the increased state due to deeper pipelines makes the chips much more complex. This increasing complexity has been viewed as one of the limits to the scalability of the super-scalar architecture. The implicit assumption in the von Neumann architecture underlies this design, therefore more radical alternatives would need to be researched if increased performance may be obtained under such constraints, for example data-flow based compilers [12,99] and computer systems [48,57]. But the data-flow architecture itself had problems: the architectural state was reflected in increasingly many registers, with increasingly many ports, thus complicating chip design, in a similar manner to the VLIW register problems.

The implementation of large quantities of memory with mixed execution units may be seen to have led to a few avenues of research. The ones that are pertinent to this thesis are:

- EARTH and CARE,

- the micro-threaded architecture,

- and cellular architectures such as IBM BlueGene/C and Cyclops.

In general these architectures examine various techniques by which the excess performance of the execution units may be used to ameliorate the relatively limited instruction and data throughput rate from the memory subsystems. Threading the program attempts to divide the sequential program into data and control dependent threads. These dependencies imply a partial execution order upon the threads that must be satisfied to maintain the consistency of the original program, as expressed by the programmer in the target language, which has often been a sequential language. By this technique the von Neumann architectural concept of strict instruction fetch-decode-execute-writeback could be avoided. Instead there could be, effectively multiple execution units, each executing as a von Neumann architecture, within a whole architecture that would be applied to the program as a whole, thus attempting to mine such ILP as may be available within that program.

#### 2.3.1 EARTH, the EARTH compiler and CARE

#### 2.3.1.1 The EARTH architecture

The EARTH architecture [53], was composed of: a synchronization processor and an execution processor, linked by two queues. The program would be written in Threaded-C, such that those threads within the program would be scheduled by an synchronization unit to execute on connected execution unit, but only if all of the related dependencies had been satisfied. Due to the multi-processor nature of the architecture the thread size would be chosen to optimize execution so that any reduction in efficiency due to long latency delays caused by inter-processor communication would be minimized. These delays could be of many orders of magnitude longer than latencies due to branch mis-predictions, or local memory accesses. Threaded-C required the programmer to annotate their program with thread constructors to direct the compiler to generate multi-threaded code.

#### 2.3.1.2 The EARTH Compiler

To overcome the necessity for the programmer to annotate the program, Tang in his work [109], describes a compiler that was able to take a C program and suitably annotate it with the appropriate threads. Most importantly this could be done without the programmer's intervention.

The technique described in [109] is as follows: the compiler tried to identify, with the potential aid of type modifiers, those operations that may have caused long latencies. Those memory accesses would be labeled using the *local* or *remote* type modifier, and if no modifier were used the compiler had to assume that the access was remote, therefore the type modifier would be *remote*. The remote type modifier indicated to the compiler that the memory access would be of long latency. These long-latency operations, for example, memory accesses or function calls, would then be split into two threads. The first thread was the original thread and the second thread contained the code that was data-dependent upon the long-latency operation. To ensure that the data dependence was satisfied a synchronization variable was introduced, such that the second thread waited upon this synchronization object before it could execute, which [109] terms as the *split-phase* constraint. To generate these threads the compiler created a data dependence graph of the input program, with the edges in the graph being labeled as remote and local. Those remote edges would be split by the compiler using the split-phase constraint. The compiler also builds up a *program dependence flow graph* in which the data and control dependencies of the program were hierarchically captured. This graph included the threaded representation of the original program from which the compiler then identified an optimal order that satisfied all of the constraints. This graph also allowed the compiler to identify further optimizations:

- To reduce thread switching costs, control and data independent threads should be merged. This was done by computing the remote level of each node, and merging those that have the same remote level.

- Within a thread, registers should be re-used and data shared with other instructions within the thread, to enhance locality and sequential performance of the instruction stream.

- Long latency operations could be covered by control and data independent local operations, providing that the overall control and data dependencies are satisfied.

In [109], Tang showed that the optimization problem posed by combining the above details and minimizing the total execution time was NP-hard. Thus an alternative partitioning algorithm was required, to minimized compilation time. Tang showed that the list-based scheduling algorithm selected was no worse than twice as slow as an optimal schedule of the nodes. This bound may be improved upon by reducing the cost of remote communication. Tang also examined the use of the various heap based analysis to aid the thread partitioner so that it can create more threads, if required.

The results presented in [109] showed that for randomly generated program graphs, the list-based, thread-scheduling algorithm produced code that was within 7% of the ideal run-time, which was close to an optimal schedule. Also, for the

custom benchmarks used by the paper, the thread scheduler produces code that was comparable in performance to optimized, hand-written code. Their results showed that the heap analysis technique improved the performance of the scheduler, which made use of the heap analysis to optimize the thread performance.

#### 2.3.1.3 The CARE Architecture

In [75] the basis of the large threads implemented within the EARTH was reexamined. In this case the threads were much reduced in size. The concept behind CARE was that the instruction fetcher within the pipeline required more guidance to be able to fetch instruction pointers to single-entry single-exit basic blocks, termed strands, that could be executed without stalls within the pipeline. Therefore during execution, the instruction fetcher would have an opportunity to identify other such strands for subsequent execution. Indeed each strand would have a set of associated firing rules that, if satisfied, would allow that strand to be scheduled for subsequent, stall-free, execution. These firing rules would represent the data and control dependencies upon which the instructions within the strand depend. Thus the instruction fetch unit would contain a set of strands that have all of their firing rules satisfied, ready to be executed, and another set of strands, which are awaiting their firing rules to be satisfied. The compiler, in this architecture, would create the strands, and identify the firing rules and populate that data structure. Moreover, the initial ordering of the strands within the instruction stream would be performed by the compiler. But the architecture, at run-time would be allowed to re-order strands, if their firing rules were satisfied.

#### 2.3.2 The Micro-Threaded Architecture

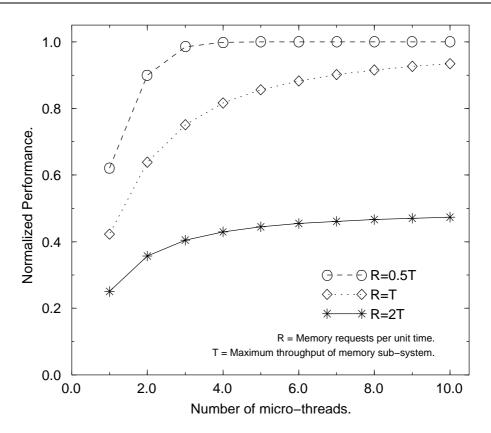

In [13] a mathematical model was presented that examined the latencies from a generalized memory unit, modeled as a queue, to a generalized processing unit, i.e. requests for data. Their results for a local memory system, as opposed to networked, are reproduced in figure 2.1. They demonstrated that to obtain over 80% performance there need only be over 4 threads ready for execution at any one instant in the program. This result was *independent* of the type of input program.

Figure 2.1: P(n) for conventional memory with  $L_0 = 1/T_0$ , taken from [13].

It was also independent of the exact memory sub-system implementation. Indeed the only assumption that was made was the fact that the processor architecture can support micro-threading, the exact implementation of the micro-threading being abstracted out of the model. From the studies of available ILP within general programs, it would seem that the implementation of the technique of micro-threading in a processor would be extremely effective in maintaining processor throughput during memory loads. An important property of the micro-threads described in [13] was that the cost of thread creation, destruction and synchronization must be very cheap, due to the number and frequent switching of micro-threads. This property of micro-threads implied that there must be efficient hardware support for them. To transform a generic program into a micro-threaded program implied that the control constraints within the sequential program must be transformed into thread creation and synchronization constraints. This task would be achieved by a microthreading stage within a suitable compiler. Further work [68] within this field has demonstrated the feasibility of such an architecture. A simple schematic of their

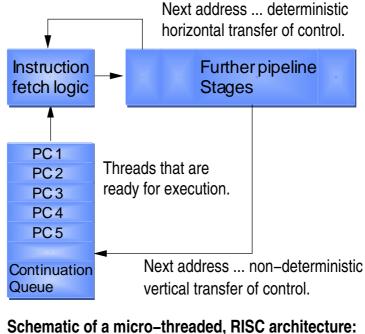

Continuation queue & transfer of control.

Figure 2.2: Schematic of a micro-threaded, RISC architecture.

implementation is provided in figure 2.2.

In this architecture, there are many very short threads, perhaps only 2-5 instructions in length. They wait upon only one data item, that may be viewed as a simplified version of the firing rules of CARE. The PCs of those threads that are ready to execute are stored in a continuation queue, for eventual execution within the pipeline. Because of the architectural speed of thread creation, synchronization and destruction, no speculation would be done: all of those features would be converted into micro-threads, thus the execution pipeline could be a relatively simple RISC-like pipeline.

#### 2.3.3 IBM BlueGene/C and Cyclops

This architecture will be discussed in much more detail in chapter 3.3 of this thesis, but for the purposes of this section, a brief summary will suffice. This architecture was a PIM-like architecture, termed cellular, that implements a number of execution units and memory units on one die. Thus it has the ability to execute many threads, has fast memory access, and may be viewed, in some sense, as between the EARTH architecture and the micro-thread architecture, in terms of a threading model.

In order to overcome the von Neumann-derived memory wall, some method of overcoming the implicit data-fetch delay should be implemented within the architecture. Moreover, such implementations usually imply multiple threads of execution, which further implies data and control dependencies that must be resolved, either at compile or run-time:

- Within EARTH and CARE this is at compile-time: the synchronization unit has explicit dependencies upon which it must wait, which have been generated at compile time.

- Within micro-threaded architectures, these dependencies may be left to be resolved at run-time, as long as all potentially data-dependent instructions are suitably annotated by the compiler.

- Within Cyclops, as will be presented in chapter 3.3, the control and data dependencies are much more complex due to the increased complexity of the architecture and the massive parallelism it makes available.

Eventually this implies that some technique must be used, either explicitly or implicitly by the programmer to generate the required threads for the architecture.

During the research program, I chose to concentrate upon the Cyclops architecture for the rest of the program, as an example of the problems with programming for such sets of threaded architectures.

### Chapter 3

# The limitations of super-scalar architectures: the memory wall

The combination of data and instruction caches effectively decouples the processor from the speed of the main-memory, by simply introducing more layers of caches in the memory hierarchy. This decoupling has been highly successful: the increase in performance of processors of the past decades has been greatly influenced by the dramatic increase in clock speed. The original 8086 was clocked at roughly 4MHz with no instruction cache, the latest Pentium 4s have been clocked at over 3.4GHz [56]. These latest Pentiums could retire instructions at a rate of roughly ten-times the main memory speed by using two to three cache levels. But to get such high speeds the pipeline depth has had to be increased. The Pentium 4 has over 20 stages; the AMD Opteron has 10-12 stages, and has been clocked at approximately 2.6 GHz. With these processors, if a branch mis-prediction or processor exception should occur and the state would have to be rolled back, then instruction fetch and the pipeline must be restarted, so it would take increasingly long in a 20 stage pipeline to begin retiring instructions after the restart. The accuracy of the branch predictor has been paramount, to avoid such time-consuming re-starts. But if the processor speed were to increase, then more stages may be needed, and branchmispredictions would become even more costly. Moreover, the increased latency of instruction fetch from the mis-predicted branch would increase due to the divergent relative speeds of the processor and main memory. This problem has been termed

the memory wall [117].

### 3.1 Multiple cores and massively parallel architectures

The problem of the memory wall may be viewed as an effect of the relative performance difference of main memory to processor speed. If the instruction throughput could be increased by reading instructions from different memory banks, then the instruction issue rate is potentially limited by the number of available memory banks, and IF stages attached to them.

Multi-core processors develop this idea. Let us suppose that the OS supports preemptive multi-tasking, and these OS-level threads are guaranteed to have the interthread, data-dependencies explicitly specified using kernel-level (thus architectural) synchronization primitives. If the resources used for developing higher clock speeds were instead used in implementing another core within the processor package, this extra core would be viewed as an extra processor by the OS for scheduling threads upon. Moreover, if the program were suitably written, it could take advantage of any extra processor resources. But this requires extensive and potentially difficult modifications to the source code to allow it to take advantage of such extra resources. Moreover, the use of OS-level threads is expensive: they have a lot of context, because each thread must not only retain the processor state, but the OS state, if it were to be context-switched off the processor. Architectural-level threading would seem to be a faster and more simple approach. Another limitation with multiple processor cores is that the processor cores take die space away from the caches and branch-predictors, that are proven, high-performance solutions.